# Vishay Foil Resistors

# Bulk Metal<sup>®</sup> Foil Technology Dual-In-Line Hermetic Resistor Networks

Vishay Model 1442, 1445 and 1446 networks incorporate all the performance features of Vishay Bulk Metal<sup>®</sup> Foil technology. The 8, 14 and 16 pin side brazed DIPs are a ceramic package. Ceramic has the advantage of electrical isolation on the underside, and, in DIP form, a favorable pin arrangement when two networks are to be placed side by side and connected together.

Review data sheet "7 Technical Reasons to Specify Bulk Metal® Foil Resistor Networks."

Networks are built to your requirements. Send your schematic and electrical requirements to the Applications Engineering Department. (See data sheet "Network Worksheet.") A unique part number will be assigned which defines all aspects of your network.

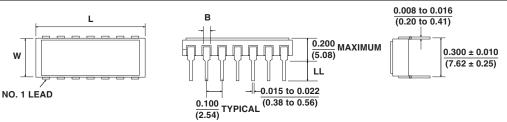

## FIGURE 1 - PACKAGE SIZES AND CHARACTERISTICS

### NOTE

- 1. These networks utilize Vishay Bulk Metal® Foil resistor chips V5X5 and V15X5 or VTF15X5 Thin Film chips.

- 2. The V5X5 and V15X5 chips have maximum resistance values of 10K and 33K respectively in Bulk Metal® Foil and 500K in VTF15X5 Thin Film chips.

- 3. The V5X5 and V15X5 chip(s) can be intermixed in a package.

| VISHAY<br>MODEL | NO. OF<br>PINS | MAXIMUM DIMENSIONS IN INCHES (MM) |                                               |                                  |                                               | CHIP<br>CAPACITY |       | MAXIMUM POWER RATING (WATTS) |

|-----------------|----------------|-----------------------------------|-----------------------------------------------|----------------------------------|-----------------------------------------------|------------------|-------|------------------------------|

| WODEL           | FINS           | L                                 | W                                             | Н                                | П                                             | V5X5             | V15X5 | AT + 70 °C                   |

| 1442            | 8              | 0.520 ± 0.020<br>(13.21 ± 0.51)   | 0.295 ± 0.010<br>(7.49 ± 0.025)               | 0.054<br>(1.37)                  | 0.125 minimum<br>(3.18)                       | 12               | 4     | 0.4                          |

| 1445            | 14             | 0.740 ± 0.045<br>(18.80 ± 1.14)   | 0.270 + 0.035/- 0.030<br>(6.86 + 0.89/- 0.76) | 0.046<br>(1.17)                  | 0.135 + 0.015/- 0.010<br>(3.43 + 0.38/- 0.25) | 30               | 10    | 1.2                          |

| 1446            | 16             | 0.780 ± 0.030<br>(19.81 ± 0.76)   | 0.290 ± 0.008<br>(7.37 ± 0.20)                | 0.040 to 0.070<br>(1.01 to 1.78) | 0.135 + 0.015/- 0.010<br>(3.43 + 0.38/- 0.25) | 36               | 12    | 1.4                          |

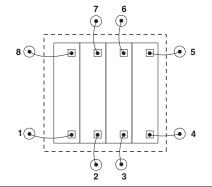

### FIGURE 2 - SAMPLE CIRCUIT DESIGN AND CHIP LAYOUT

## NOTE:

Usable area is represented by the dotted lines - a rectangle 0.150 Inches x 0.200 Inches. Illustrations not to scale. Chips shown undersize for clarity. Drawing view is from the top looking down into the package.

#### FIGURE 3 - SAMPLE CIRCUIT DESIGNS AND CHIP LAYOUTS NOTE: Usable area is represented by the dotted lines - a rectangle 0.150 Inches x 0.500 Inches. Illustrations not to scale. Chips shown undersize for clarity. Drawing view is from the top looking down into the package. TWO DECADES OF BCD LADDER **FOUR DIVIDERS PLUS TEN RESISTOR DIVIDER APPLICATION RESISTOR PLUS TWO SCALING RESISTORS** R10 R1 R2 R3 R4 R5 R6 R7 R8 R9 R1 R2 R3 R4 R5 R6 R7 R8 R9 R1 R2 R3 R4 R5 R6 R7 R8 R9 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 13 ₹R9₹R10 R1 R2 R3 R4 R5 R6 R7 R8 ₹R1 **₹R3 ₹R5** ₹ R7 R9 }R4 }R6

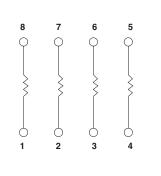

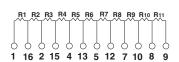

## FIGURE 4 - SAMPLE CIRCUIT DESIGNS AND CHIP LAYOUTS

### NOTE:

Usable area is represented by the dotted lines - a rectangle 0.150 Inches x 0.600 Inches. Illustrations not to scale. Chips shown undersize for clarity. Drawing view is from the top looking down into the package.

ELEVEN RESISTOR DIVIDER

3 12

EIGHT RESISTOR PACKAGE

# **Legal Disclaimer Notice**

Vishay Precision Group

# **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Precision Group, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay Precision Group"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay Precision Group disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay Precision Group's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay Precision Group.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay Precision Group products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay Precision Group for any damages arising or resulting from such use or sale. Please contact authorized Vishay Precision Group personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 63999 www.vishaypg.com Revision: 22-Feb-10